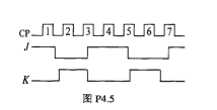

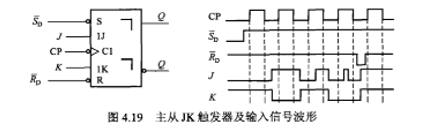

更多“主从JK触发器输入信号波形如图4.19所示,试画出主触发器输…”相关的问题

更多“主从JK触发器输入信号波形如图4.19所示,试画出主触发器输…”相关的问题

第2题

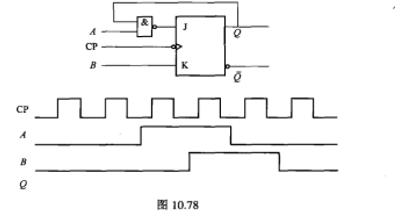

触发器电路及输入信号A、B波形如图10.78所示.在连续输入6个时钟脉冲CP下,画出Q对应的波形.(设Q

触发器电路及输入信号A、B波形如图10.78所示.在连续输入6个时钟脉冲CP下,画出Q对应的波形.(设Q

点击查看答案

起始为0态)

第5题

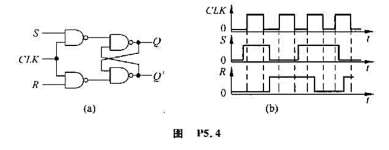

画出图P5.4(a)中电平触发SR触发器Q和Q'端的电压波形。时钟脉冲CLK和输入S、R的电压波形如图P5.

画出图P5.4(a)中电平触发SR触发器Q和Q'端的电压波形。时钟脉冲CLK和输入S、R的电压波形如图P5.

点击查看答案

4(b)所示。设触发器的初始状态为Q=0。

第6题

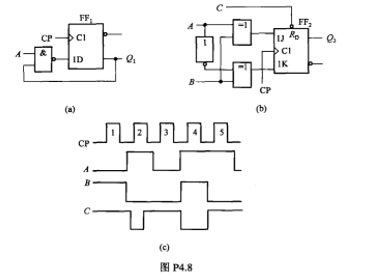

TTL边沿触发器组成的电路分别如图P4.8(a)和(b)所示,其输入波形如图P4.8(c)所示,试分别画出Q1

TTL边沿触发器组成的电路分别如图P4.8(a)和(b)所示,其输入波形如图P4.8(c)所示,试分别画出Q1和Q2端的波形.设各电路的初始状态均为0.

第7题

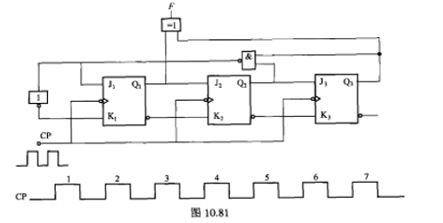

逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出Q1、Q2、Q3和F的对应波形.(各

逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出Q1、Q2、Q3和F的对应波形.(各

点击查看答案

触发器起始均为0态)

第8题

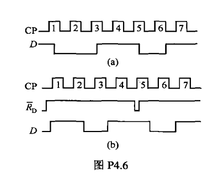

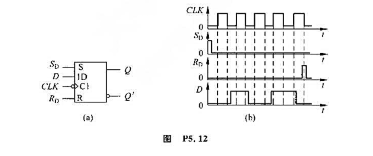

在图P5.12(a)下降触发D触发器中,已知时钟脉冲CLK、输入端D、异步置位输入端RD和异步复位输入端RD的

在图P5.12(a)下降触发D触发器中,已知时钟脉冲CLK、输入端D、异步置位输入端RD和异步复位输入端RD的电压波形如图P5.12(b)中所示,试画出输出端Q对应的电压波形。

第9题

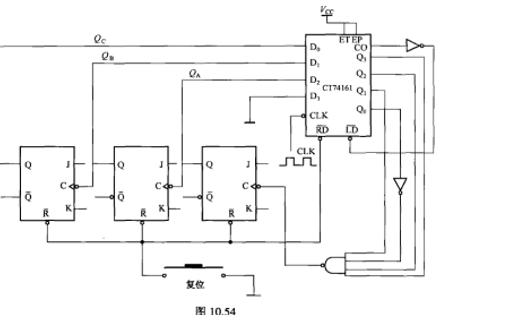

如图10.54所示逻辑电路.开始工作时按一下复位开关进入初始状态,分析该电路.(1)描述电路逻辑功

如图10.54所示逻辑电路.开始工作时按一下复位开关进入初始状态,分析该电路.(1)描述电路逻辑功

点击查看答案

如图10.54所示逻辑电路.开始工作时按一下复位开关进入初始状态,分析该电路.

(1)描述电路逻辑功能;

(2)简要描述电路中CT74161,JK触发器及门电路的作用;

(3)当连续输入33个CLK脉冲后,74LS161的状态编码Q3Q2Q1Q0=(2)B及触发器的状态编码QCQBQA=()B.

如果结果不匹配,请

如果结果不匹配,请