更多“3-8译码器有()个译码输出。”相关的问题

更多“3-8译码器有()个译码输出。”相关的问题

第1题

关于译码器说法()不正确。

A.2-4译码器有2个输入端4个输出端

B.3-8译码器中的3是指输出端有3个

C.译码器是组合逻辑电路

D.译码是指将具有特定含义的二进制码转换成对应的输出信号

第2题

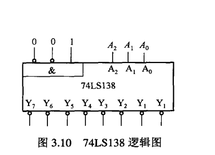

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一个全减器;设Ai为被减数,Bi为减数,低位向该位的借位为小差为Di向高位借位为Ji+1.

(1)列出全减器真值表;(2)写出函数逻辑表达式;(3)画出实现逻辑电路图.

第4题

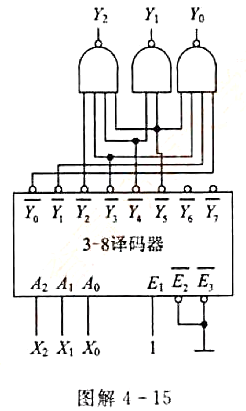

某组合电路的输入X和输出Y均为三位二进制数。当X<2时,Y=1;当2≤X≤5时,Y=X+2;当X>5时,Y=0。

某组合电路的输入X和输出Y均为三位二进制数。当X<2时,y=1;当2≤x≤5时,y=x+2;当x>5时,Y=0。试用一片3-8译码器和少量逻辑门实现该电路。

点击查看答案

第5题

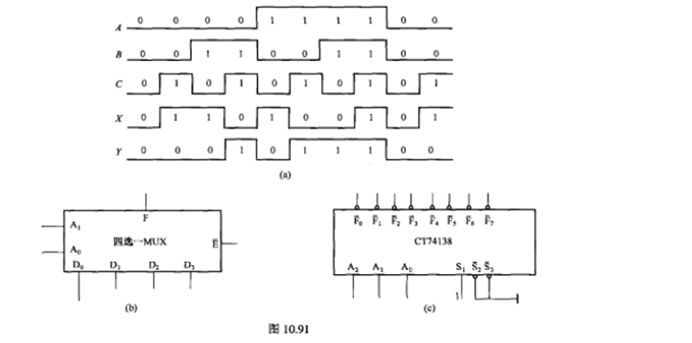

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

点击查看答案

逻辑功能,并分别用基本逻辑门电路、四选一MUX数据选择器(如图10.91(b))和3-8译码器(如图10.91(c))实现此逻辑电路.

第11题

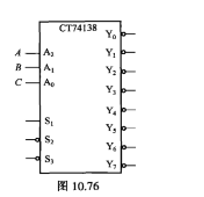

用3-8译码器74LS138(见图10.76)和与非门实现逻辑函数.

用3-8译码器74LS138(见图10.76)和与非门实现逻辑函数.

点击查看答案

用3-8译码器74LS138(见图10.76)和与非门实现逻辑函数 .

.

如果结果不匹配,请

如果结果不匹配,请