题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

今有3位计数器,其8个译码输出不允许有毛刺,应该如何设计编码?写出最低位D型触发器的输入逻辑表达式。如果该计数器仅允许有7种状态,是否有可能保证译码器的输出不产生毛刺?

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“今有3位计数器,其8个译码输出不允许有毛刺,应该如何设计编码…”相关的问题

更多“今有3位计数器,其8个译码输出不允许有毛刺,应该如何设计编码…”相关的问题

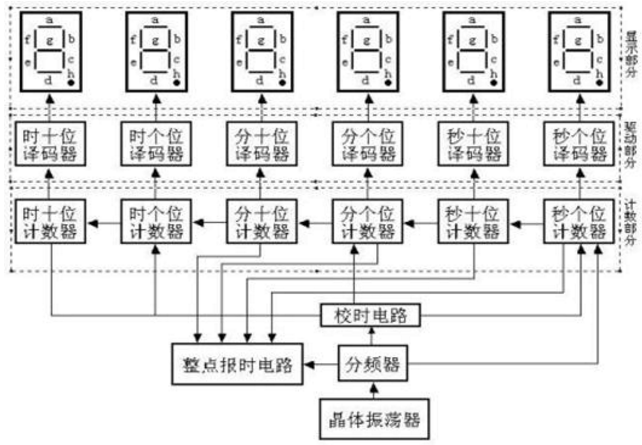

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

A.2-4译码器有2个输入端4个输出端

B.3-8译码器中的3是指输出端有3个

C.译码器是组合逻辑电路

D.译码是指将具有特定含义的二进制码转换成对应的输出信号

A.2-4译码器有2个输入端4个输出端

B.3-8译码器中的3是指输出端有3个

C.译码器是组合逻辑电路

D.译码是指将具有特定含义的二进制码转换成对应的输出信号

5,Jacky : 90

for i in range(10):

print('{:____},{:____}:{:____}'.format(i, name[i], score[i]))请填入最简单的形式。